Cache 之间的一致性

多核系统中 Cache 不一致

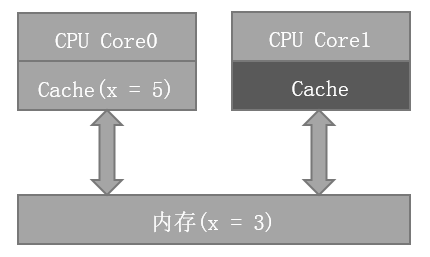

假设内存中有一个数据 x,值为 3,被缓存到 Core0 和 Core1 的各自 Cache 中,这时 Core0 将 x 改为 5,如果 Core1 不知道 x 已经被修改,还在使用旧值,就可能导致程序出错,这就是 Cache 之间不一致。如下图所示:

Cache 之间一致性的底层操作

为了保证 Cache 之间的一致性,处理器提供了两个保证 Cache 一致性的底层操作:Write invalidate 和 Write update。

Write invalidate(写无效):当一个核修改了一份数据,其他核上如果缓存了这份数据,就置无效(invalid)。

假设 2 个核都使用了内存中的变量 x,Core0 将它修改为 5,Core1 就将自己对应的 Cache line 置成无效(invalid)。如下图所示:

Write update(写更新):当一个核修改了一份数据,其他核上如果缓存了这份数据,就都更新到最新值。如下图所示:

Write invalidate 是一种简单的方式,不需要更新数据,如果所有核以后不再使用变量 x,采用 Write invalidate 就非常有效。不过由于一个 valid 标志对应一个 Cache line,将 valid 标志置成 invalid 后,这个 Cache line 中其他的原本有效的数据也将不能使用。Write update 会产生大量的数据更新操作,不过只要更新修改的数据,如果所有核都会只用变量 x,那么 Write update 就比较有效。由于 Write invalidate 简单,大多数处理器都使用 Write invalidate。

京公网安备11010802043204号

京公网安备11010802043204号