SD 系统架构

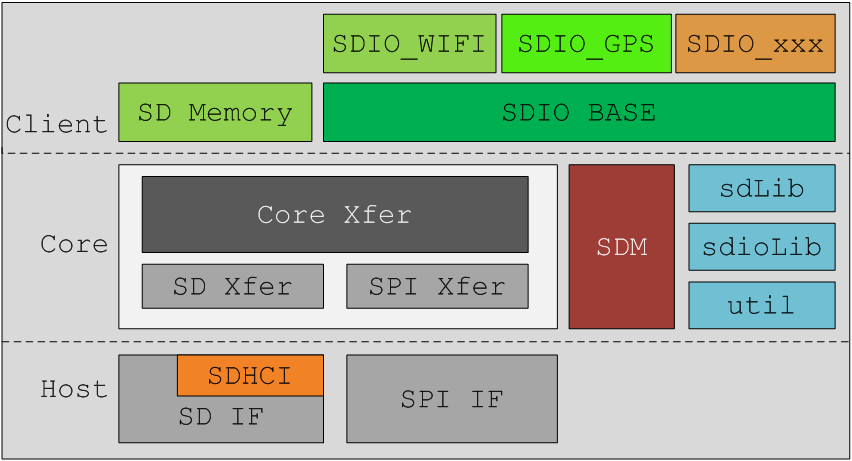

SylixOS 中 SD 协议栈(以下称作 SD Stack)结构如下:

Host 层:硬件控制器抽象层,SD 控制器在不同的硬件平台上可能有不同的实现,因此需要实现具体的传输处理操作。所有的控制器驱动都向上(Core 层)提供统一的操作接口。SD Stack 已经提供了符合 SD 规范的标准控制器 SDHCI 驱动,在此情况下,控制器驱动的编写将更加简单。当然也可使用 SPI 传输。

Core 层:主要封装了 SD 和 SPI 两种传输方式以及 SD Memory 和 SDIO 相关协议操作库,让 Client 层只需要关心与具体设备相关的 SD 协议处理,而不必考虑底层的硬件情况,详细介绍如下:

- sdLib 为基于 Core Xfer 为传输对象封装的 SD Memory 相关协议操作库。

- sdioLib:与 sdLib 一样,是针对 sdio 类设备特殊操作的相关工具库,sdio 类设备驱动使用此库可以使驱动的编写更简单。

- SDM:SD DRV Manager, 即 SD 驱动管理层,这里的 SD 驱动包括 SD 设备驱动和 SD 控制器驱动,这样两者的信息都由 SDM 管理维护,以此达到两者完全隔离的目的。

Client 层:实现具体的设备类协议,主要包括 SD Memory 和 SDIO BASE 两个库,分别对应 SD 存储卡类设备和 SDIO 类设备,详细介绍如下:

- SD Memory 负责 SD Memory 相关的协议处理(如初始化,块读写等),它同时完成与 SylixOS 块设备相关的接口创建(BLK_DEV)。

- SDIO BASE:sdio 类基础驱动,它和 SD Memory 处于同一级别,它不会直接去创建实际的 sdio 类设备,主要是在完成 sdio 的基础初始化后,使用特定的 sdio 子类驱动来创建对应的设备。之所以设计 sdio 类基础驱动,是为了让驱动的管理更加统一,同时将原设计中的一些缺点(比如设备驱动要关心 Host 的一些信息)掩藏起来, 让 sdio 类设备驱动开发更简洁。

SD 总线定义为一主多从总线,理论上一条总线上可以挂接多个 SD 从设备,它们以不同的地址区分。但 SylixOS SD 协议实现上,并不支持一条 SD 总线上存在多个设备的情况,原因有以下几点:

- 由于 SD 卡接口完全兼容 MMC 卡,因此若同一个总线上同时存在 SD 卡和 MMC 卡,且它们需要不同的电压支持时,不论是硬件还是软件上都很难处理此类情行。

- 当一个总线上挂接多个 SDIO 类设备时,如何有效区分产生的 SDIO 中断来自于哪个设备目前还未能找到任何答案。

- 总线上的多个 SD 设备若需要不同的传输速率,SD 规范中也没有给出任何可行的解决方案,因为 SD 控制器本身不能处理不同速率带来的时序转换问题(这里可以对比一下 USB 总线,不同速率的设备是通过 HUB 完成传输转换的)。因此 SD 规范中也明确说明了,在高速模式下,一个 SD 控制器只能对应一个 SD 设备。

- SD 规范没有对一个总线上可同时挂接的设备最大数量进行明确的定义,它可能受限于端口的驱动能力,硬件设计上的抗干扰能力等因素,这增加了应用的不确定性。

- 硬件成本越来越低,实际的应用中也少有此类需求。很多芯片上都同时存在多个 SD 硬件控制器通道,这已经能满足需要同时使用多个 SD 设备的场合。

可见在这一点上,SD 总线的定义存在诸多缺陷。基于以上几点原因,SylixOS SD 协议在软件实现上,一个 SD 控制器仅能同时支持一个 SD 设备。同时也建议设计硬件电路时,最好不要将多个 SD 卡槽挂接到一个 SD 总线上,因为即使是 Linux 系统,也是同样的处理方式。

京公网安备11010802043204号

京公网安备11010802043204号