PCI 总线简介

PCI 总线发展

PCI(Peripheral Component Interconnect)总线的诞生与 PC 的蓬勃发展密切相关。在处理器架构中,PCI 总线属于局部总线。局部总线作为系统总线的延伸,其主要功能是连接外部设备。处理器主频的不断提升,要求速度更快、带宽更高的局部总线。PCI 总线推出后,迅速统一了当时并存的各类局部总线,EISA、VESA 等其他 32 位总线很快就被 PCI 总线淘汰了。

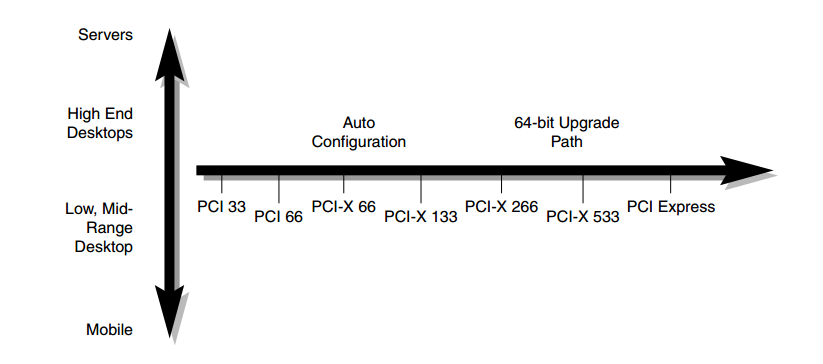

PCI 总线规范由 Intel 的 IAL 提出,是一种并行总线,随后 PCISIG (PCI Special Interest Group)陆续发布了 PCI 总线的 V2.2、V2.3 规范,并最终将规范定格在 V3.0。从数据宽度上看,PCI 总线有 32bit、64bit 之分;从总线速度上分,有 33MHz、66MHz 两种。改良的 PCI 系统,PCI-X,最高可达到 64bit、133MHz,这样就可以得到超过 1GB/s 的数据传输速度,当采用 Quad Data Rate 技术时,甚至可以得到超过 4GB/s 的速度。

目前 PCI-E 是 PCI 最新的发展方向,串行,点对点传输,各个传输通道独享带宽;支持双向传输模式和数据分通道传输;在 PCI-E 3.0 规范中,X32 端口的双向传输速率搞到 320Gbps,可以满足新一代的 I/O 接口,如千兆、万兆的以太网技术、4G/8G 的 FC 技术。

PCI 目前的多维度应用如下图所示。

PCI 总线结构

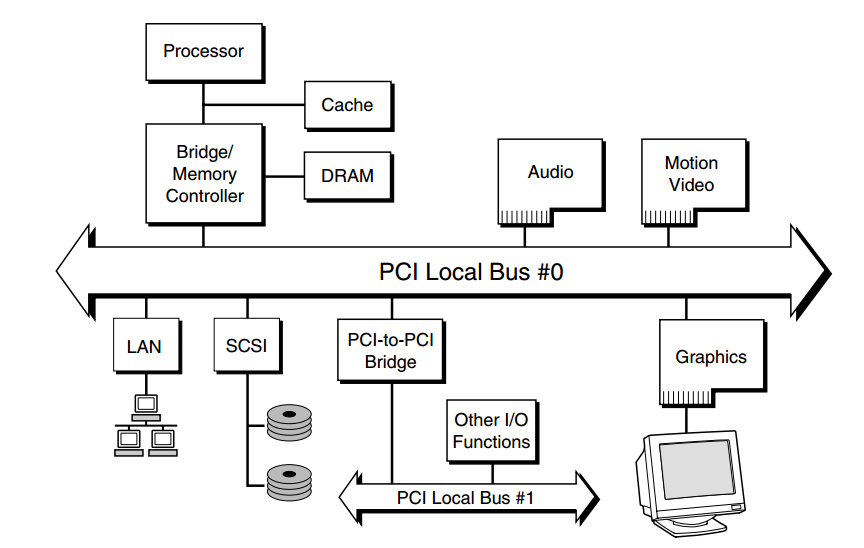

PCI 总线作为处理器的局部总线,是处理器系统的一个组成部件,下图显示了典型的 PCI 本地总线系统架构。该示例并不是任何具体的架构。在该示例中,与 PCI 总线相关的模块包括:HOST 主桥、PCI 总线、PCI 桥和 PCI 设备。PCI 总线由 HOST 主桥和 PCI 桥推出,HOST 主桥与主存储器控制器在同一级总线上,因此 PCI 设备可以方便地通过 HOST 主桥访问主存储器,即进行 DMA 操作。

在 PCI 总线中有三类设备:PCI 主设备、PCI 从设备和桥设备。其中 PCI 从设备只能被动地接收来自 HOST 主桥或者其他 PCI 设备的读写请求;而 PCI 主设备可以通过总线仲裁获得 PCI 总线的使用权,主动地向其他 PCI 设备或者主存储器发起存储器读写请求。而桥设备的主要作用是管理下游的 PCI 总线,并转发上下游总线之间的总线事务。HOST 主桥是一个很特别的桥片,其主要功能是隔离处理器系统的存储器域与处理器系统的 PCI 域,管理 PCI 总线域,并完成处理器与 PCI 设备间的数据交换。

一个 PCI 设备可以既是主设备也是从设备,但是在同一个时刻,这个 PCI 设备只能是其中一种。PCI 总线规范将 PCI 主从设备统称为 PCI Agent 设备。一个 PCI 设备可以包含 2~8 个功能,每个功能称为一个逻辑设备。因此 PCI 总线中,一个 PCI 设备通过 PCI 总线 ID,设备 ID 以及功能 ID 进行唯一标示。

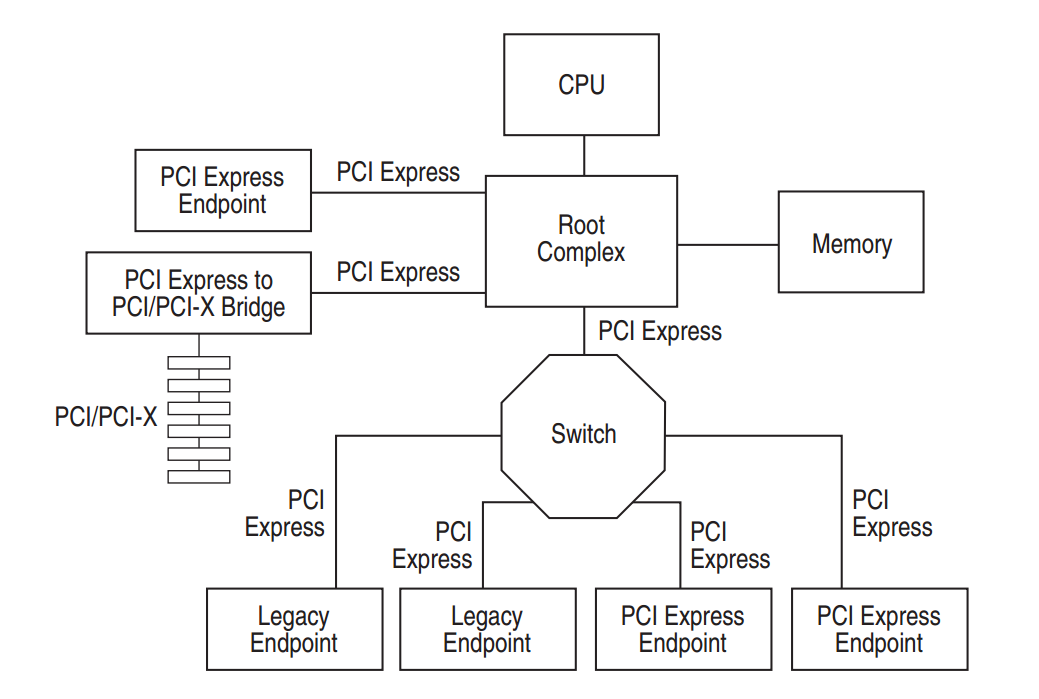

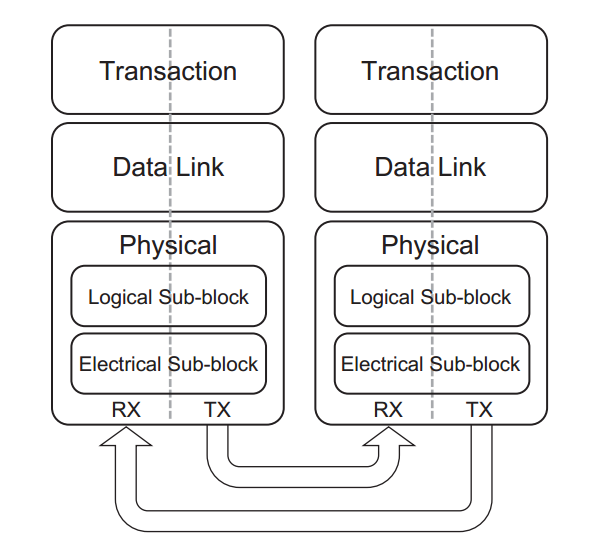

PCI 总线使用并行总线结构,在同一条总线上所有外部设备共享总线带宽,而 PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条 PCIe 链路中只能连接两个设备。这使得 PCIe 和 PCI 总线采用的拓扑结构有所不同,如下图所示。PCIe 总线除了在连接方式上与 PCI 总线不同之外,还具有多个层次,发送端发送数据时将通过这些层次,而接收数据时也使用这些层次。

PCI 总线信号定义

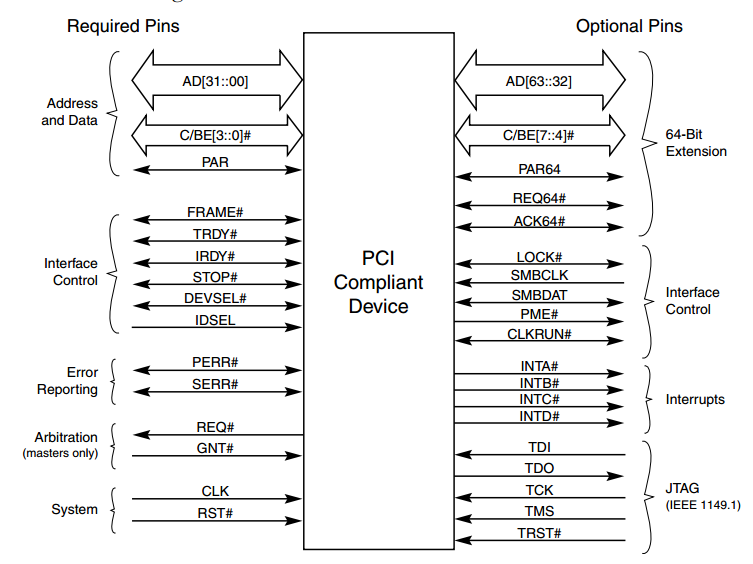

PCI 的引脚信号如下图所示,这里除了中断信号不做过多介绍,详细信息可参考 V3.0 规范手册。PCI 总线提供了 INTA#、INTB#、INTC#和 INTD#四个中断请求信号,PCI 设备借助这些中断请求信号,使用电平触发方式向处理器提交中断请求。当这些信号为低时,PCI 设备将向处理器提交中断请求;当处理器执行中断服务程序清除 PCI 设备的中断请求后,PCI 设备将该信号置高,结束当前中断请求。PCI 总线规定单功能设备只能使用 INTA#信号,而多功能设备才能使用 INTB#/C#/D#信号。

与 PCI 不同,PCIe 总线的物理链路的一个数据通路(Lane)中,有两组差分信号,共 4 根信号线,如下图所示。PCIe 链路可以有多条 Lane 组成,目前 PCIe 链路可以支持 1、2、4、8、12、16 和 32 个 Lane,即 ×1、×2、×4、×8、×16 和 ×32 宽度的 PCIe 链路。每一个 Lane 上使用的总线频率与 PCIe 总线使用的版本有关。

PCI 配置空间

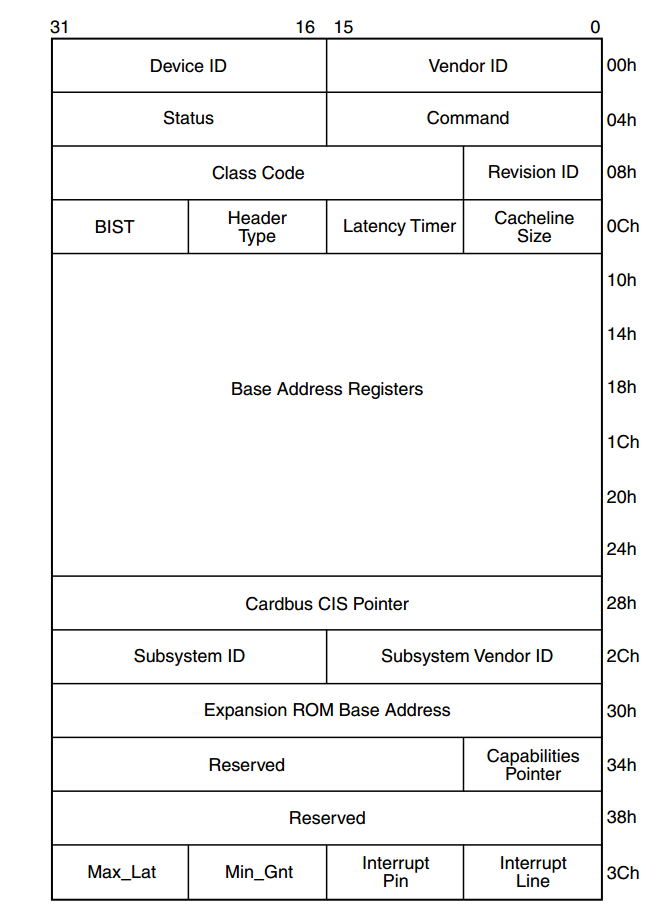

PCI 设备都有独立的配置空间,里面存储了一些基本信息,如生产商、IRQ 中断号以及 mem 空间和 I/O 空间的起始地址和大小等,HOST 主桥通过配置读写总线事务访问这段空间。PCI 总线规定了三种类型的 PCI 配置空间,分别是 PCI Agent 设备使用的配置空间,PCI 桥使用的配置空间和 Cardbus 桥片使用的配置空间。本小节只介绍 PCI Agent 的配置空间,而并不介绍 PCI 桥和 Cardbus 桥片使用的配置空间。

在 PCI Agent 设备空间中包含了许多寄存器,这些寄存器决定了该设备在 PCI 总线中的使用方法,本节不会全部介绍这些寄存器,因为系统软件只对部分配置寄存器感兴趣。PCI Agent 设备使用的配置空间如下图所示。

- Device ID 和 Vendor ID 寄存器:该组寄存器的值由 PCISIG 分配,只读。其中 Vendor ID 代表设备的生产厂商,而 Device ID 代表这个厂商所生产的具体设备。

- Revision ID 和 Class Code 寄存器:该组寄存器只读。其中 Revision ID 寄存器记载 PCI 设备的版本号。该寄存器可以被认为是 Device ID 寄存器的扩展。而 Class code 寄存器记载 PCI 设备的分类。

- Capabilities Pointer 寄存器:在 PCI 设备中,该寄存器是可选的,但是在 PCI-X 和 PCIe 设备中必须支持这个寄存器。Capabilities Pointer 寄存器存放 Capabilities 寄存器组的基地址,PCI 设备使用 Capabilities 寄存器组存放一些与 PCI 设备相关的扩展配置信息。

- Interrupt Line 寄存器:该寄存器是系统软件对 PCI 设备进行配置时写入的,记录当前 PCI 设备使用的中断向量号。设备驱动程序可以通过这个寄存器,判断当前 PCI 设备使用处理器系统中的哪个中断向量号,并将驱动程序的中断服务例程注册到操作系统中。

- Interrupt Pin 寄存器:该寄存器保存 PCI 设备使用的中断引脚。PCI 总线提供了四个中断引脚:INTA#、INTB#、INTC#和 INTD#。Interrupt Pin 寄存器为 1 时表示使用 INTA#引脚向中断控制器提交中断请求,为 2 表示使用 INTB#,为 3 表示使用 INTC#,为 4 表示使用 INTD#。

- Base Address Registers 寄存器:该组寄存器简称为 BAR 寄存器,BAR 寄存器保存 PCI 设备使用的地址空间的基地址,该基地址保存的是该设备在 PCI 总线域中的地址。其中每一个设备最多可以有 6 个基址空间,但多数设备不会使用这么多组地址空间。

- Command 寄存器:该寄存器为 PCI 设备的命令寄存器,在初始化时,其值为 0,此时这个 PCI 设备除了能够接收配置请求外,不能接受任何存储器或者 I/O 请求。系统软件合理设置该寄存器之后,才能访问该设备的存储器或 I/O 空间。

- Status 寄存器:该寄存器的绝大多数位都是只读位,保存 PCI 设备的状态。

除了上述所有 PCI 设备必须支持的 0x00~0x3F 基本配置空间,PCI/PCI-X 和 PCIe 设备还扩展了 0x40~0xFF 这段配置空间,在这段配置空间主要存放一些与 MSI 或者 MSI-X 中断机制和电源管理相关的 Capability 结构体。其中所有能够提交中断请求的 PCIe 设备,必须支持 MSI 或者 MSI-X Capability 结构。

PCIe 设备还支持 0x100~0xFFF 中断扩展配置空间。PCIe 设备使用的扩展配置空间最大为 4KB,在 PCIe 总线的扩展配置空间中,存放 PCIe 设备所独有的一些 Capability 结构,而 PCI 设备不能使用这段空间。

其中每一个 Capability 结构都有唯一的 ID 号,每一个 Capability 寄存器都有一个指针,这个指针指向下一个 Capability 结构,从而组成一个单项链表结构,这个链表结构的最后一个 Capability 结构的指针为 0,如下图所示。

京公网安备11010802043204号

京公网安备11010802043204号